# Applications of VLSI Design in Artificial Intelligence and Machine Learning

[1]\*Imran Ullah Khan, [2]Nupur Mittal and [3]Mohd. Amir Ansari

[1]iukhan@iul.ac.in, [2]mittal@iul.ac.in and mamir@iul.ac.in

[1,2]Department of Electronics & Communication Engineering, Integral University, Lucknow

In the advanced time CMOS based organizations like semiconductor and gadgets face extreme scheduling of products and different other pressures. For resolving this issue, electronic design automation (EDA) must provide "design-based equivalent scaling" to continue the critical industry trajectory. For solving this problem machine learning techniques should be used both inside and "peripherally" in the design tools and flows. This article reviews machine learning opportunities along with physical implementation of IC will also be focussed. Cloud intelligence-enabled machine learning-based data analytics has surpassed the scalability of current computing technologies and architectures. The current methods based on deep learning are inefficient, require a lot of data and power consumption, and run on a data server with a long delay. With the advent of self-driving cars, unmanned aerial vehicles and robotics, there is a huge need to analyze only the necessary sensory data with low latency and low power consumption on edge devices. In this discussion, we will talk about effective AI calculations, for example, fast least squares, binary and tensor convolutional neural organization techniques, and comparing prototype accelerators created in FPGA and CMOS-ASIC chips. Planning on future RRAM gadgets will likewise be momentarily depicted.

# I. INTRODUCTION

Rapid growth in IC technology is catching up with IC design capabilities, mainly due to the significant advancement in artificial intelligence. The computational tasks assigned to VLSI are time-consuming processes but when AI is implemented to perform the same computational tasks required time will be reduced. As technology advances rapidly, VLSI developers must observe and implement this growth to enhance their design tools. Improved design methods, features, and capabilities bring the promise of AI to VLSI design. Although artificial intelligence brings many features and methods, it still has certain limitations to bring solutions to various problems. Thus, the introduction of machine learning (ML) offers many opportunities for improvement in collaboration or individual fields of VLSI and computerbased design. By using AI chips are designed and implemented. It is seen as the premier application of artificial intelligence. In present scenario, computer-based design tools frequently used with knowledge gained from introductory AI courses. Previously chips were mostly hand-designed, the chip size was too large, and the performance was slow. Validating those chips based on hand-designed designs is a complex task. These complexities lead to the development of automated tools. The automation tool has been upgraded for other tasks assigned to it. Researchers bring new design methods from time to time, such as memory combinations, new programs in computing tasks, etc., which need to be automated in the design process. Companies like Intel, IBM, etc. have in-house CAD facilities for these purposes. Cadence, Synopsys, Mentor Graphics, and many others sell CAD tools, which can be thought of as the application of artificial intelligence to chip design. Sometimes data obtained or collected from clusters is mandatory for identifying patterns. Such patterns can be effectively identified by focusing on things such as classifying various objects, predicting objects of interest, input-output relationships based on their complexity, deep neural networks with various other layers for each patterns, objects and speech recognition applications. Machine learning is of great interest in the above fields. DNNs need to respond to new things by comparing with already suggested things or existing methods. This must be extended to the most recent stage of development. If it is any kind of non-stationary system, the decision-making process needs to be adjusted to strengthen the action process, which is a result of machine learning.

In the former times huge computers made up of large size vaccum tubes used. Although they were hailed as the fastest computers of their time, they certainly didn't stand a chance compared to modern machines. Modern computers are getting smaller, faster, cheaper, more powerful, and more efficient with every second of progress. But what's driving this change? The whole computing field ushered in a new Dawn of electronic miniaturization with the advent of Bardeen's (1947-48) semiconductor transistor and Shockley's (1949) bipolar transistor at Bell Labs. The development span of microelectronics is shorter than the average lifespan A human expectation, but it has seen as many as four generations. In the early 1960s, low-density manufacturing processes were classified as small scale integration (SSI), where the number of transistors was limited to around 10.

This rapidly gave way to Medium Scale Integration (MSI) in the late 60's when around 100 transistors could be placed on a single chip. Transistor-Transistor Logic (TTL), which proposed higher integration densities, also withstood the Emitter-Coupled Logic (ECL) of other IC families and became the basis for the first integrated circuit revolution. It was the founding of this family that inspired semiconductor giants such as Texas Instruments, Fairchild, Motorola and National Semiconductor. The early seventies marked the development of transistor counts to around 1000 per chip, known as large scale integration (LSI). By the mid-1980s, the number of transistors on a single chip had exceeded 1,000, ushering in the era of very large scale integration (VLSI). Although many improvements have been made and transistor counts are still increasing, further generation names, eg. ULSI (Ultra Large Scale Integration) is generally avoided. It was during this time that TTL was defeated in the battle against the MOS (Metal Oxide Semiconductor) family, because the same issues that slapped the vacuum tube into slack, power consumption, and its limit on the number of gates that could be positioned on a single die. The second era of the integrated circuit revolution began with the launch of the first microprocessors, Intel's 4004 in 1972 and the 8080 in 1974. Today, companies such as Texas Instruments, Infineon, Alliance Semiconductors, Cadence, Synopsys, Cisco, Micron, National Semiconductor, STMicroelectronics, Qualcomm, Lucent, Mentor Graphics, Analog Devices, Intel, Philips, Motorola and many others It has been proven and committed to many areas of VLSI, such as programmable logic devices, hardware description languages, design tools, embedded systems, etc.

## II. ARTIFICIAL INTELLIGENCE

Artificial intelligence is the field of computer science that focuses on creating machines that can engage in behaviors that humans perceive as intelligent. The ability to create intelligent machines has fascinated humans since ancient times, and now with the advent of computers and 50 years of research into artificial intelligence programming techniques, the dream of intelligent machines is becoming a reality. Researchers are creating systems that can mimic human thinking, understand speech, beat the best human chess players, and countless other feats never before done [2].

# III. ARTIFICIAL INTELLIGENCE & VLSI (AI AND VLSI)

Most of the thriving applications of artificial intelligence (AI) in integrated circuit and printed circuit board design schematics are in the field of expert systems acting as design assistants [3][9]. But AI covers only one aspect of expert technology. VLSI design is a complex process. Moreover, that complexity is multi-dimensional. Others include the layered nature of the design process and self-design. AI language helps solve such complex problems. These language features, combined with expert systems, provide an important first step towards solving very difficult problems, namely verifying the correctness of the design [3].

# III. APPLICATIONS OF AI

Uses of AI are developing quickly. These are being sought after in college research as well as in modern conditions like in industries. Field of VLSI design adapting AI rapidly[7][8][11]. The first important application is the expert system. An expert system is essentially a computer program that simulates the behavior of a human expert by applying reasoning techniques to the knowledge base of a specialized domain. Expert systems should be able to solve immediate and moderately difficult problems in professional field. Expert system should be able to provide one or more solutions of each difficulty. These alternatives should be reliable. Expert systems differ from standard computer programs in several important ways. In traditional computer programs, "intelligence" is written directly into the code. The code then solves the problem by executing an algorithm known to solve the problem. In expert systems, "intelligence" is separate from the control or reasoning part. Without changing the control portion changes and additions to the knowledge can be done[4]. The main feature of knowledge-based approaches used in artificial intelligence is to ask human experts what knowledge is used in solving certain tasks, and to develop algorithms and data structures that can explicitly represent that knowledge. Researchers using this method in many areas of VLSI have found some advantages over trivial methods, such as those discussed in [4].

- Making incremental improvements will be easier by using this method.

- For the system it is easier to explain what it is doing and why

- ➤ It is easier for human experts to identify where the system's knowledge is incorrect or incomplete and explain how to fix it.

- Easier to use human experts' abilities interactively

In VLSI design these experts system are being used widely [7][8][10][12]. One of the first knowledge-based systems created for VLSI design was Design Automation Assistant (DAA). It plays an important role in VLSI. It was developed jointly by researchers at Carnegie-Mellon University and AT&T Bell Labs. Rules describing various synthesis operations contained in the original DAA. Production rules were expressed in terms of registers, operators, data paths, and control signals. The DAA system has been continuously expanded and refined over the years[3]. More than 500 rules are present in its data base which are used in designing of several systems. Design Advisor by NCR [3] acts an expert assistant. The role of design advisor is to provide the advice in six areas for the design of semi-custom CMOS chips from a library of standard cells.

An expert system shell called Proteus, which is developed by the Microelectronics and Computer Technology Corporation (MCC). Design Advisor is built on top of Proteus. Next knowledge based system named REDESIGN [4].Redesign is being used by several people to address the following problem of functional redesign. It helps the user identify changes in the circuit so that it can meet the changed functional specification without introducing unwanted side effects. In this case, intelligent assistance is required for two completely different types of reasoning for a given circuit. The first basic type of reasoning about circuits is causal reasoning about the interrelationships between signals within a circuit. This is an overview of the concepts of circuit simulation and symbolic simulation. It involves tasks such as, given a description of

the input data flow to a component, derive a description of the output data flow. Alternatively, given a specification of the required properties of the component's output, determine which properties the component's input must satisfy. The REDESIGN subsystem developed to solve such problems is called CRITTER[6]. The second type of reasoning essential to redesign involves reasoning about the purpose of the component. For example, given a circuit and its specification, explain the role that specific components play in achieving the overall specification. Or, identify a range of components that can be substituted for that component without violating the overall specification.

Machine Learning: The use and development of computer systems that are able to learn and adapt without following explicit instructions, by using algorithms and statistical models to analyse and draw inferences from patterns in data.

[13] Machine learning also includes Artificial intelligence. Machine learning covers very vast area in medicine, email filtering, speech recognition, and computer vision. For many uses ,develop traditional algo is not possible. The solution is machine learning [15,16]. The application of machine learning to biological databases has increased.

A part of machine learning is closely related to computational statistics, which focuses on using computers to make predictions; but not all machine learning is statistical learning. Data mining is a related field of study which focuses on unsupervised learning. Biological brains is also a very important application of machine learning [17][18].

#### APPLICATIONS OF ML

Role of ML in manufacturing process

With the help of ML a manufacturer can achieve real benefits such as:

Increase the efficiency and decrease the costs the industry area can be optimized with the help of machine learning. In the case of Google, the company reduced its data center electricity usage by 40% by using custom ML .Google also tried to reduce it manually but that improvement was not acheived.Google is not a single company so many companies adopted ML. Using machine learning to improve internal operational efficiency, more than 80% say it helps them reduce costs.

Reducing maintenance costs and improving reliability Use machine learning to create optimized maintenance schedules based on actual equipment usage.

. In the same way customers will also be benifited, offering them personalized maintenance plans. Using machine learning to more accurately predict customer demand, a textile manufacturer was able to reduce inventory levels by 30%, allowing it.By ML inventory levels and waste can also be reduced.

Enhancing new design, With the help of ML consumer exactly know the application of product. If the product fails so any one can know the reason behind it. These problems can be fed back to the team and the team will remove all the problems with the help of machine learning. By using ML reasearchers can enhance their R&D capabilities.

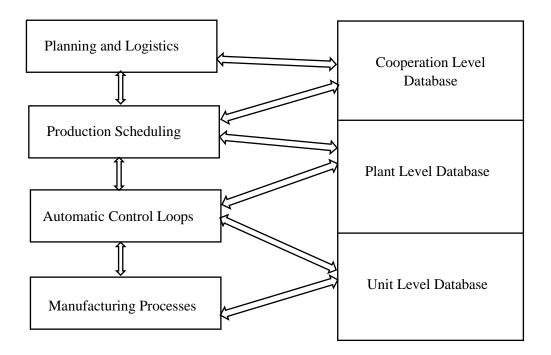

Fig. 1. Hierarchical applications of data analytics and machine learning in process industries. Role of ML in mask Synthesis

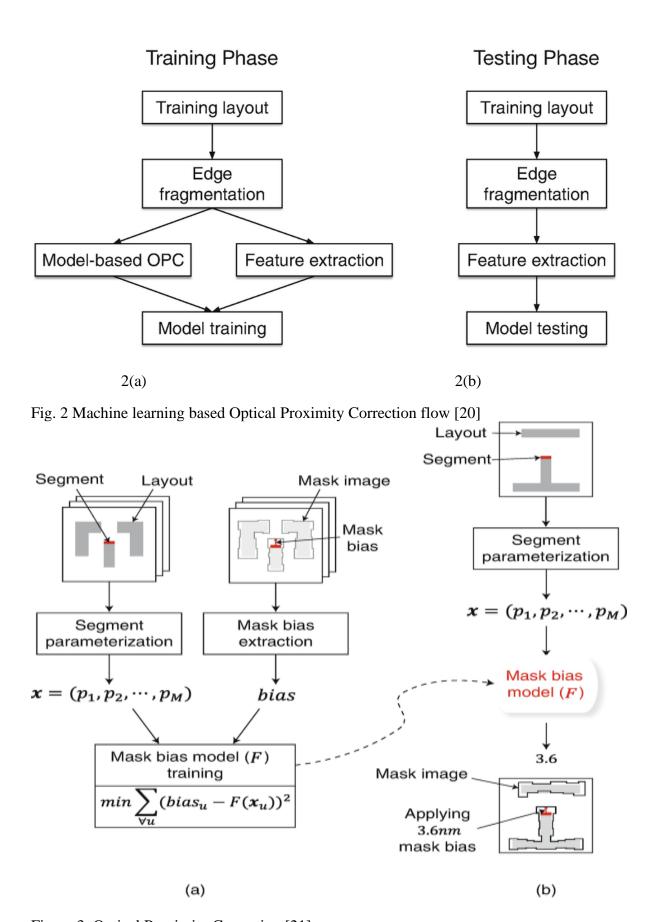

As technology nodes expand to the limits of optical wavelengths, various resolution enhancement techniques (RET), such as optical proximity correction (OPC), source mask cooptimization, and sub-resolution assist functions (SRAF), become a necessity. For improving turnaround time for mask synthesis Machine learning will be adopted by various RETs.

Figure 2 gives a standard mask synthesis flow in which target patterns (layout) are taken as input and mask patterns are generated after iterative optimization procedures including SRAF generation, OPC, mask rule check (MRC) and lithography compliance check (LCC) [19]. In SRAF generation, a sub-resolution assist function is inserted to facilitate the printing of target patterns. In OPC, the edge portion of the target pattern is optimized for robust lithography. To ensure mask fabrication friendliness, mask fabrication rules should be checked after these optimization procedures in MRC. LCC then performs lithography simulations under a set of process windows to check printability.

Here process windows denote different {focus, dose} conditions to generate printing contours, such as nominal, inner, and outer contour, as shown in Fig. 2(b). To quantify the process window, two metrics are introduced: Edge Placement Error (EPE) assesses the distance between the target pattern profile and the nominal profile; Process Variation (PV) Band assesses the area between the inner and outer profiles. A typical goal of RET is to minimize the EPE and PV bands.

Figure 3: Optical Proximity Correction [21]

#### IV. APPLICATIONS IN PHYSICAL DESIGN

This part will incorporate a few critical utilizations of pattern matching and AI in physical design (counting physical verification).

# A. Lithography Hotspot Detection

This part will incorporate a few critical utilizations of pattern matching and AI in physical design. A hotspot has been located by hotspot detection problem on a given layout with quick turnaround time. Pattern images using complicated lithography models has been obtained using conventional lithography simulation [22]. In spite of the fact that it is exact, full-chip lithography simulation is computationally costly and, in this way, we can't give quick criticism to direct early physical design stages. Area of hotspot identification assumes a significant part in spanning the immense role among modeling and process aware physical design. A great deal of machines learning based hotspot identification works. Machine learning methods build a relapse model in light of a bunch of preparing information. This strategy can normally recognize past obscure hotspot. Be that as it may, it might produce false alarm, which are not genuine hotspot. Step by step instructions to further develop the recognizing precision is the principal challenge while taking on machine learning methods. Numerous new methodologies use SVM and ANN strategies to develop the hotspot discovery kernel. In [23], 2D distance change and histogram extraction on pixel-based design pictures for building SVM-based hotspot recognition are examined.

# A.2 Pattern Matching Approach

Design matching-based techniques are likewise generally applied in hotspot identification. A format diagram is proposed in [23] to reflect pattern related CD variety. The outcome chart can be utilized to observe hotspot including shut highlights, L-shaped elements and complex examples. The idea of range design [24] is proposed to consolidate process-subordinate particulars, and is upgraded in [25] to address new kinds of hotspot. A reach design is a 2-D format of square shapes with extra determinations encoded by strings. Each reach design is related with a scoring process to show the hazardous areas as per yield effect. The hotspot designs are put away in a pre-characterized library and the location interaction performs string matching to track down hotspot. This approach is exact, yet the development of range pattern depends on a grid-based format framework, and might be tedious when the quantity of grid is huge. Yu et al. [26] propose a DRC-based hotspot recognition by removing basic topological elements and demonstrating them as design rules. Hence, hotspot identification can be seen, when in doubt, really taking a look at process through a DRC engine. In [27], an example matching based hotspot characterization conspire is proposed. The hotspot are grouped into bunches by data mining techniques. The delegate hotspot in each bunch is then recognized and put away in a hotspot library for future hotspot identification. The hotspot grouping approach in [27] depends on a distance metric of various example tests, which is characterized as a weighted integral over the region where a couple of hotspot designs contrasts (XOR of examples). It is touchy to the little varieties or movements of the shapes. In [28], an Improved Tangent Space (ITS) based measurement is proposed for hotspot grouping. It is an augmentation of the all-around created tangent space strategies [29,30] in computer vision community. The ITS measurement characterizes a distance metric of a couple of polygons, which is the L2 standard of the distinction of the comparing turning elements of the polygons [29] [30]. The turning capacity of polygon estimates the angle of the counter clockwise tangent as an element of the standardized circular length, estimated from some reference point of the polygon. The ITS based measurement is not difficult to register and is tolerant with little varieties or movements of the shapes. With the ITS based measurement, the hotspot

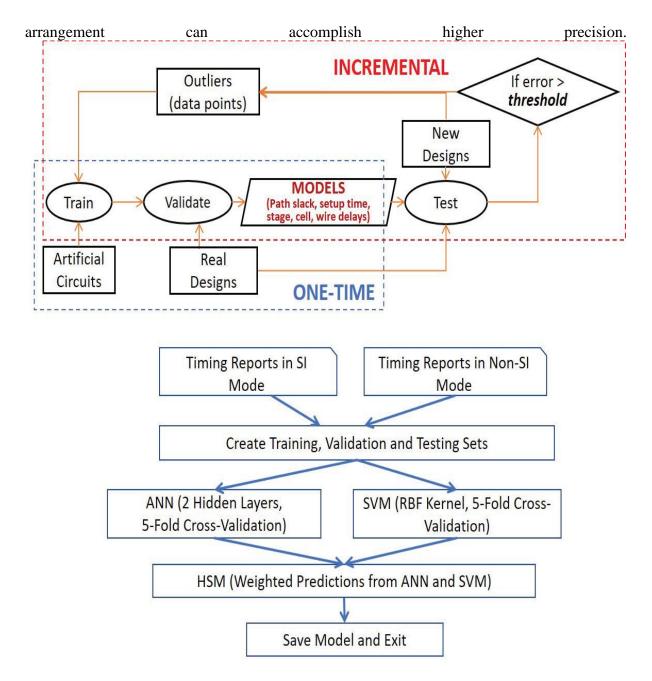

Figure 4: Flow and results for machine learning of Static Timing Analysis tool miscorrelation [32-35]

#### Role of ML in Data path Placement

S. Ward et al [12], proposed a programmed data path extraction in the accompanying new manner. Makes a decision about the various data path and afterward allots the positions to them to streamline it. This improvement is continued in an overall approach to driving or putting the data alongside new position stream fig 5.1[12]. SVM and ANN techniques are consolidated at the underlying training stage to segregate and pass judgment on the data path. This makes a proficient model during run time and treated as a reduced model when both the strategies are joined together. From the arrangement of working data path a fault tolerant is fixed in SVM model. In any case, ANN will create the choices from the trained samples and it is like organization of neurons presents in people. Whether it is data path or non-data path, exactness of assessment is the superb point. This can be accomplished by both SVM and ANN.

Distinguishing the data path design from obscure design is further developed which can met in the data learning models in the preparation stage. Certain edge levels are set while involving SVM and AVM assessment to recognize the specific example is data path design or non-data path design.

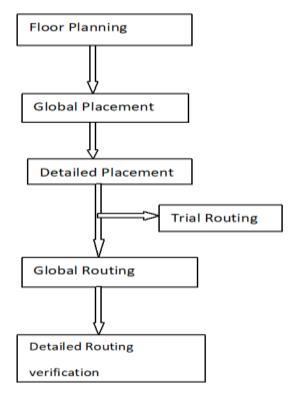

Role of ML on Rout ability Prediction:

The work [36] materials the main calculated study on rout capacity forecast in light of Convolutional Neural Network. Subconsciously, that is clearly a promising course however isn't all around concentrated beforehand. The method, Route Net can just estimate general rout ability fig 5 in conditions of Design Rule Violation count thinking about macros. Route Net accomplishes tantamount accuracy in contrast with that of worldwide routing however is by and large significant degrees speedier really assuming preparation period is regularly counted. To the best of our agreement, this is really the first root capacity predictor which incorporates both such extraordinary exactness and incredible speed. In anticipating DRC hotspot regions considering macros, it makes a huge improvement of half precision improvement versus worldwide routing. Moreover, Route Net remarkably outflanks SVM and calculated regression-centered expectation.

Figure 5: General Physical design flow [36]

## **Conclusion:**

This paper we have shown the utilization of Artificial Intelligence in different parts of VLSI Logical and Physical plan like the utilization of AI in assembling, miscorrelation, power investigation, testing, mask synthesis, transition and interconnect delay, CAD instruments. However there are a lot of extents of AI in VLSI design stages. Additionally, VLSI backend design is currently at its starting stage in applying AI systems. For instance, in the SRAF age, pixel-by-pixel assumption is required and simply direct models are used, limiting the use of more convoluted models as a result of high computational expense. Basically, OPC is just sensible to embrace direct models moreover. Such kind of progress issues fundamentally need to make another cover picture with a given format picture. It justifies exploring whether

generative learning procedures can be applied. For plan and coordinating issues, manual assurance of critical features is at this point is still expected, while it isn't apparent whether general depiction of arrangement data exists and whether customized incorporate decision can be made. Besides, not at all like fields with expansive assessment on AI like picture affirmation in which tremendous proportion of data is open, it is generally irksome and expensive to secure adequate data in VLSI plan for planning strong and exact models. Thusly, it is essential to make methodologies to improve showing precision with relaxed need of colossal data so AI can be by and large embraced. These difficulties stay to be investigated in future.

#### REFERENCES

- [1] Engineers Garage, Web: http://www.engineersgarage.com/articles/vlsi-design-future, Accessed on: 30 September 2012.

- [2] Oracle ThinkQuest, Web: http://library.thinkquest.org/2705/, Accessed on: 30 September 2012.

- [3] Ann Miller, "From Expert Assistant to Design Verification: Applications of AI to VLSI Design", Session 11Al, IEEE, Vol.2, pp.406-410, 1989.

- [4] Louis I. Steinberg, Tom M. Mitchell, "A knowledge based approach to VLSI CAD the redesign system", In Proceedings of the 21stDesign Automation Conference, IEEE Press, Piscataway, NJ, USA, pp.412-418, 1984.

- [5] T. J. Kowalski, D.E. Thomas, "The VLSI Design Automation Assistant Prototype System", In 20th Design Automation Conference, IEEE, pp.479-483, 1983.

- [6] Van E. Kelly, "The CRITTER System: Automated Critiquing of Digital Circuit Designs", In Proceedings of the 21st DesignAutomation Conference, IEEE Press, 1984, 419-425.

- [7] R. L. Steele, "An Expert System Application in Semicustom VLSI Design", In Proceedings of the 24th ACM/IEEE DesignAutomation Conference, A. O'Neill and D. Thomas (Eds.), ACM, pp.679-688, 1987.

- [8] H. Farahat, A. Eldessouki, M. Y. Mahmoud, H. Elsimary, "An Expert System for VLSI Layout Design", International Conference on Systems Engineering, IEEE, pp.529-532, 1989.

- [9] M. Stefik, L. Conway, "Towards the Principled Engineering of Knowledge", AI Magazine, Vol. 3:3, pp.4-16, 1982. (Reprinted inReadings From the AI Magazine, Volumes 1-5, 1980-1985, pp.135-147, 1988.)

- [10] J. Kim, J.P. McDermott, "TALIB: An IC Layout Design Assistant", In Proc. AAAI, pp.197-201, 1983.

- [11] Guy Rabbat, "VLSI and AI are getting closer", Circuits and Devices Magazine, IEEE, Vol.4, No.1, pp.15-18, 1988.

- [12] T.J. Kowalski, D. J. Geiger, W.H. Wolf, W. Fichtner, "The VLSI Design Automation Assistant: From Algorithms to Silicon", Design & Test of Computers, IEEE, Vol.2, No.4, pp.33-43, 1985.

- [13] Mitchell, Tom (1997). Machine Learning. New York: McGraw Hill. ISBN 0-07-042807-7, OCLC 36417892.

- [14] Koza, John R.; Bennett, Forrest H.; Andre, David; Keane, Martin A. (1996). Automated Design of Both the Topology and Sizing of Analog Electrical Circuits Using Genetic Programming. Artificial Intelligence in Design '96. Springer, Dordrecht. pp. 151–170. doi:10.1007/978-94-009-0279-4\_9.

- [15] Hu, J.; Niu, H.; Carrasco, J.; Lennox, B.; Arvin, F., "Voronoi-Based Multi-Robot Autonomous Exploration in Unknown Environments via Deep Reinforcement Learning" IEEE Transactions on Vehicular Technology, 2020.

- [16] Bishop, C. M. (2006), Pattern Recognition and Machine Learning, Springer, ISBN 978-0-387-31073-2.

- [17] Friedman, Jerome H. (1998). "Data Mining and Statistics: What's the connection?". Computing Science and Statistics. 29 (1): 3–9.

- [18] Zhou, Victor (2019-12-20). "Machine Learning for Beginners: An Introduction to Neural Networks". Medium. Retrieved 2021-08-15.

- [19] Lin, Y., Xu, X., Ou, J., Pan, D.Z.: Machine learning for mask/wafer hotspot detection and mask synthesis. In: Photomask Technology, vol. 10451, p. 104510A. International Society for Optics and Photonics (2017).

- [20] Matsunawa, T., Yu, B., Pan, D.Z.: Optical proximity correction with hierarchical bayes model. Journal of Micro/Nanolithography, MEMS, and MOEMS 15(2), 021,009–021,009 (2016).

- [21] Chan, Tuck-Boon, Andrew B. Kahng, Jiajia Li, and Siddhartha Nath. 2013"Optimization of overdrive signoff." In 18th Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 344-349. IEEE.

- [22] D. Ding, 1. A. Torres, and D. Z. Pan, "High performance lithography hotspot detection with successively refined pattern identifications and machine learning," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), pp. 1621-1634,2011.

- [23] J. -Y Wuu, E G. Pikus, A. Torres, and M. Marek-Sadowska, "Rapid layout pattern classification," in IEEEIACM Asia and South Pacific Design Automation Coriference (ASPDAC), 2011, pp. 781-786.

- [24] Y-T. Yu, G.-H. Lin, l. H.-R. Jiang, and e. Chiang, "Machine-learning based hotspot detection using topological classification and critical feature extraction," in IEEEIACM Design Automation Coriference (DAC), 2013, pp. 671-676.

- [25] Z. Xiao, Y Du, H. Tian, M. D. Wong, H. Yi, H.-S. P Wong, and H. Zhang, "Directed self-assembly (DSA) template pattern verification," in IEEE/ACM Design Automation Conference (DAC), 2014, pp. 1-6.

- [26] J.-R. Gao, B. Yu, and D. Z. Pan, "Accurate lithography hotspot detection based on PCA-SVM classifier with hierarchical data clustering," in Proceedings of SPIE, vol. 9053, 2014.

- [27] B. Yu, 1.-R. Gao, D. Ding, X. Zeng, and D. Z. Pan, "Accurate lithography hotspot detection based on principal component analysis-support vector machine classifier with hierarchical data clustering," 10urnal of Micro Nanolithography, MEMS, and MOEMS (1M3), vol. 14, no. 1, p. 011003,2015.

- [28] J. Guo, E Yang, S. Sinha, C. Chiang, and X. Zeng, "Improved tangent space based distance metric for accurate lithographic hotspot classification," in IEEE/ACM Design Automation Conference (DAC), 2012, pp. 1173-1178.

- [29] E. M.Arkin, L. Chew, D. P.Huttenlocher, K. Kedem, and J. S.B.Mitchell, "An efficiently computable metric for comparing polygonal shapes," IEEE Transactions on Pattern Analysis and Machine Intelligence, no. 3, pp. 209-216, 1991.

- [30] L. J. Latecki and R. Lakamper, "Shape similarity measure based on correspondence of visual parts," IEEE Transactions on Pattern Analysis and Machine Intelligence, no. 10, pp. 1-6,2000.

- [31] S. -Y Lin, J.-Y Chen, J.-C. Li, w.-Y Wen, and S.-e. Chang, "A novel fuzzy matching model for lithography hotspot detection," in IEEE/ACM Design Automation Coriference (DAC), 2013, pp. 681-686.

- [32] S. S. Han, A. B. Kahng, S. Nath and A. Vydyanathan, "A Deep Learning Methodology to Proliferate Golden Signoff Timing", Proc. DATE, 2014, pp. 260:1-260:6.

- [33] A. B. Kahng, B. Lin and S. Nath, "Enhanced Metamodeling Techniques for High-Dimensional IC Design Estimation Problems", Proc. DATE, 2013, pp. 1861-1866.

- [34] A. B. Kahng, B. Lin and S. Nath, "High-Dimensional Metamodeling for Prediction of Clock Tree Synthesis Outcomes", Proc. SLIP, 2013, pp. 1-7.

- [35] A. B. Kahng, M. Luo and S. Nath, "SI for Free: Machine Learning of Interconnect Coupling Delay and Transition Effects", Proc. SLIP, 2015, pp. 1-8.

- [36] Xie, Zhiyao, Yu-Hung Huang, Guan-Qi Fang, Haoxing Ren, Shao-Yun Fang, Yiran Chen, and Jiang Hu.2018 "RouteNet: Routability prediction for mixed-size designs using convolutional neural network." In IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pp. 1-8.